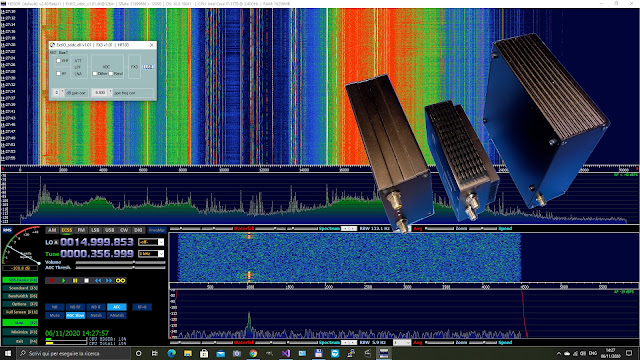

ExtIO_sddc.dll v1.01

It is a tentative version of ExtIO_sddc.dll that can operate with BBRF103, HF103, RX888 as the FX3 Arm code detects the hardware type used.

The sources are at https://github.com/ik1xpv/ExtIO_sddc/releases

a compiled dll is at https://drive.google.com...

MD5 ef1579eeb47ee1fc4f3c8ec45520d81c extio_sddc_v1.01.dll

Copy the dll in a directory with HDSDR.exe and libfftw3f-3.dll.

Here a summary of changes.

- First, there are a lot of new bugs... I'm sure :-)

- The SDDC_FX3.img arm program detects the radio hardware.

If there is not a programmable Si5351a the radio is a HF103 and operates only in HF

else

if there is a pull up (led blue) on GPIO54 of FX3 the radio is a BBRF103

else

it is a RX888.

-The control protocol in between FX3 and ExtIO_sddc.dll is redesigned and the

programming of Si5351a and R820T2 is now made by the SDDC_FX3.img code.

It obtains faster communication and simplifies the ExtIO a little bit.

-The ExtIO_SDDC.dll dialog is minimalistic. Are there the antenna bias T controls, the Dith and Rand ADC controls.

( I think to remove Dith and Rand from future releases as they seem to me useless now. ?)

Calibration controls for gain (+/- 20dB) and frequency reference (+/- 200 ppm) are in the dialog.

The frequency reference calibration is made in software and operates on Si5351a pll in BBRF103 and RX888. In HF103 it changes the nominal ADC_FREQ and requires restart of HDSDR to set.

- The switching of HF and VHF modes and IF bandwidths is faster and possibly more reliable.

- To avoid the VLF mode tuning switch I moved the spectrum 1 MHz up so that now the tuning in HF is from -1MHz to 31MHz so that the useful band is 0-30 MHz.

- The R820T2 gains are controlled via a single control.

This is a video of HF103:

Here a RX888 video:

I cannot understand. If the frequency of the SiS can be NOT adjusted but CHANGED. This mean can I put clock frequency at 40 MHz and respectively ADC sampling speed of 40 MSps? I need different bandwidth and it makes no sense to have 64 MSps when flow is high and you just do not need such flow? did you finally intend to publish so named software model of this device? Mean all registers, IDs, addresses, end points, commands etc.

ReplyDeleteIf we have a reference given by a quartz at Fs 63.998 MHz instead of the nominal at 64 Mhz, this means that the ADC input sample rate is 63.998 Msps. The decimation is an integer ratio and therefore the bands are Fs/2 ..FS/ 32= 31.999 ... 1.9999375 MHz. If we inform HDSDR that these are the values we use, the tuning frequency and scales indicate the exact frequency of the received signals, taking into account the real frequency of the reference. This allows you to use non-trimmerable reference oscillators. If have an exact frequency reference or a trimmable one the correction is not needed and is set to zero.

DeleteCurrently a program restart is required to inform HDSDR that the correction value has changed.

Hello, I do not us it for SDR but for sampling HF signal. So What's happened after output and ExtIo I don't know and don't care. Idea is that I need to set SiS to 96 Msps/sec and have input Bandwidth only to 48 MHz .My signal is up to 6 MHz and I need to oversampling it 8x for better processing - its long discussion why is not good idea to sample signal at Nyquist/Cotelnikov limit. So you say that there are no problem to set SiS clock at 96 MHZ ( Msps/sec) and have 48 MHz Bandwidth

DeleteAlso I still await somebody to publish software model (which mean end point, register address, register value, end similar) that allow EVERYBODY to make his own driver for windows or module/device for Linux.

This comment has been removed by a blog administrator.

ReplyDeletenice

ReplyDeleteAberrant DSP SketchCassette crack

ReplyDeleteI am very impressed with your post because this post is very beneficial for me.