Down sampling more

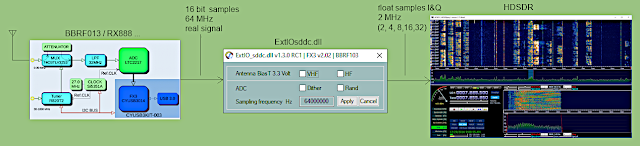

ExtIO_sddc.dll is designed for use of BBRF103 / RX888 with HDSDR . The input stream from the ADC ( 16bit , 64 MHz real signal) is analyzed in an overlap and save method (overlap-scrap) with an FFT of dimension N = 8192 . After the low pass filtering convolution an output FFT - 1 of dimension M = 256 decimates the sampling rate to 2 MHz . 64 * 256 / 8192 = 2 MHz. Signal tuning is made with circular shift in frequency and fine tuning using a complex mixer in time. This is a simplified diagram of SDDC: If we want to use a stand alone application deeper decimation and filtering is required to match the computer audio sampling. A possible block diagram of the application is: The Base Band Digital Processor module receives an I&Q input at 2 MHz and generates an output to demodulation module at "audio" speed.. Here some numbers. /* F INPUT FFT FFT ...